## AU8530: Power Line Smart AC Switch Controller

### **General Description**

The AU8530 is a patented high voltage AC switch controller device that monitors incoming line voltage to ensure that the downstream load only runs at its safe maximum continuous voltage ratings. In the case of an over-voltage line scenario, the AU8530 will shut the AC switch to safeguard and isolate the load, thereby decreasing the possibility of catastrophic failure.

During the recovery timer interval (which the user can adjust with an external timing capacitor), normal load operation will resume in the subsequent cycle and be aligned to zero Lineto-Load voltage condition. This results in minimal in-rush current stress And this process continues until the line voltage has stabilized back within safe operating range.

The AU8530, with a 16 V output drive, is the optimal control device for any kind of competitively priced IGBT. Furthermore, to accommodate a broad range of applications, the device is also packaged in a handy compact form factor SOIC-8.

### **Features**

- User adjustable maximum load voltage

- Timing pin for programmable recovery delay

- Line-to-Load voltage monitoring

- Low energizing current 60 µA (typical)

- 'In-cycle' Over-Voltage load isolation

- Suitable for use with IGBT AC switch

- Zero-volt (Line-to-load) AC switch connect

- Zero-volt (Line-to-load) AC switch disconnect

- Compatible with 50 Hz/240 V and 60 Hz/110 V

- Output gate drive voltage of 16 V

- Line to Neutral voltage monitoring

- SOIC 8-pin package

### **Applications**

- White Goods, Home Appliances

- Motor Control & Protection

- Air Conditioners

- Delicate Electronics

- Servers and Data Routers

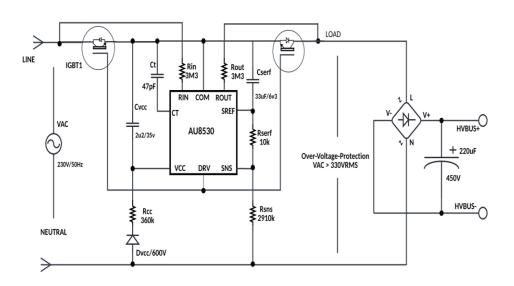

Figure 1 AU8530 Typical Application Diagram

## **Table of Contents**

| General Description1          |

|-------------------------------|

| Features1                     |

| Applications1                 |

| Table of Contents             |

| List of Tables                |

| List of Figures4              |

| 1 Pin Configuration           |

| 1.1 Pin Configuration Diagram |

| 1.2 Pin Description           |

| 2 Electrical Characteristics  |

| 3 Functional Description      |

| 3.1 VCC PIN                   |

| 3.2 SERF PIN                  |

| 3.3 RIN/ROUT PINS             |

| 3.4 SNS PIN                   |

| 3.5 CT PIN                    |

| 3.6 DRV PIN                   |

| 4 Thermal Dissipation         |

| 5 Package Description         |

| 6 Ordering Information        |

| 6.1 Top Marking14             |

| 7 Revision History            |

## **List of Tables**

| Table 1 AU8530 Pin Description                  | 5  |

|-------------------------------------------------|----|

| Table 2 Absolute Maximum Ratings <sup>[1]</sup> | 6  |

| Table 3 Recommended Operating Conditions        | 6  |

| Table 4 Electrical Characteristics              | 6  |

| Table 5 ESD Ratings                             | 7  |

| Table 6 Thermal Characteristics                 | 7  |

| Table 7 AU8530 Ordering Information             | 14 |

| Table 8 Revision History                        | 15 |

# **List of Figures**

| Figure 1 AU8530 Typical Application Diagram      | 1  |

|--------------------------------------------------|----|

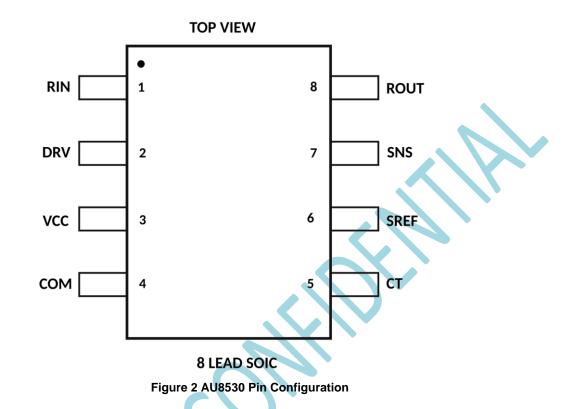

| Figure 2 AU8530 Pin Configuration                | 5  |

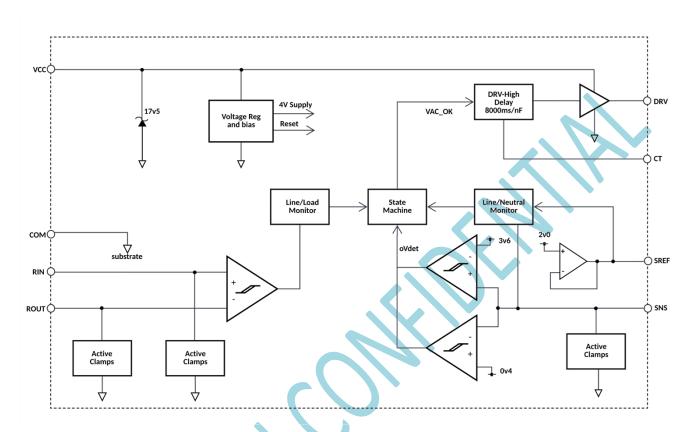

| Figure 3 Functional Block Diagram                | 8  |

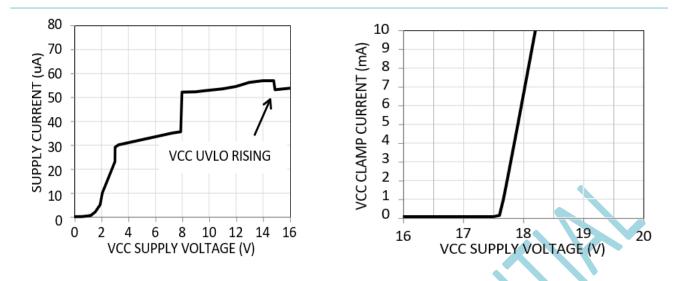

| Figure 4 VCC Operating and Clamping Current      | 9  |

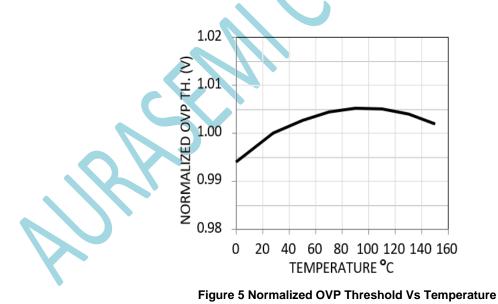

| Figure 5 Normalized OVP Threshold Vs Temperature | 9  |

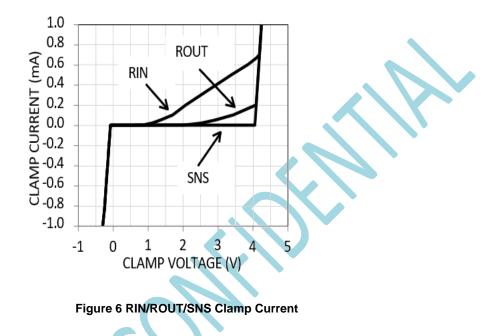

| Figure 6 RIN/ROUT/SNS Clamp Current              | 10 |

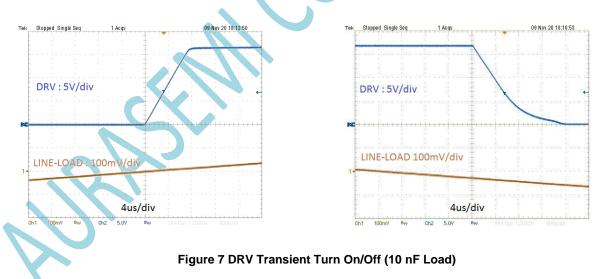

| Figure 7 DRV Transient Turn On/Off (10 nF Load)  | 11 |

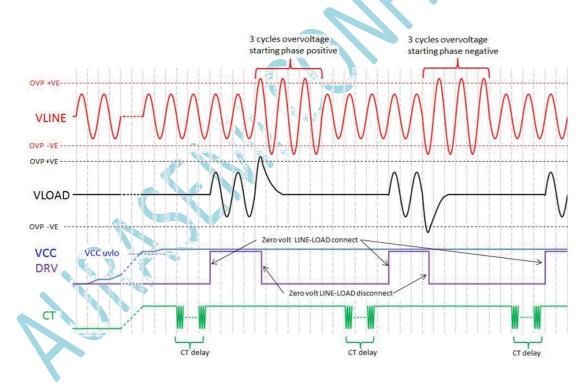

| Figure 8 Over-Voltage Protection Timing Example  | 12 |

| Figure 9 AU8530 SOIC 8                           |    |

| Figure 10 AU8530 Top Marking                     | 14 |

# **1 Pin Configuration**

# **1.1 Pin Configuration Diagram**

## **1.2 Pin Description**

Table 1 AU8530 Pin Description

| Pin Name | Pin No. | Description                                                                                                              |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------|

| RIN      | 1       | Positive sense input for line-to-load monitor (external resistor to Line side)                                           |

| DRV      | 2       | Output driver to control IGBT gate                                                                                       |

| VCC      | 3       | Supply bias voltage input                                                                                                |

| СОМ      | 4       | Ground reference point for all voltages (connect to IGBT common emitter point)                                           |

| СТ       | 5       | Restart timing delay control (external capacitor to COM pin)                                                             |

| SREF     | 6       | Sense reference pin for Line-Neutral monitor (connect with 33 $\mu F$ capacitor to COM pin and 10 K resistor to SNS pin) |

| SNS      | 7       | Sense input voltage for overvoltage monitoring (external resistor to Neutral)                                            |

| ROUT     | 8       | Negative sense input for Line-to-load monitor (external resistor to Load side)                                           |

|          |         |                                                                                                                          |

## **2 Electrical Characteristics**

#### Table 2 Absolute Maximum Ratings<sup>[1]</sup>

| Parameter              | Pin                      | Min  | Тур   | Max | Units |

|------------------------|--------------------------|------|-------|-----|-------|

|                        | VCC, DRV                 | -0.3 |       | 20  | V     |

| Power Supply           | RIN, ROUT, CT, SNS, SREF | -0.3 |       | 5.5 | V     |

| Clamping Current       | VCC to COM               | 0    |       | 20  | mA    |

|                        | RIN, ROUT, SNS           | -2   |       | 2   | mA    |

| Operating Junction Ten | nperature                | -40  |       | 150 | °C    |

| Storage Junction Temp  | erature                  | -65  |       | 150 | °C    |

| MSL Level              |                          |      | MSL 1 |     |       |

|                        |                          |      |       |     |       |

Notes:

1. Exceeding maximum ratings may shorten the useful life of the device. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to- ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J (MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

| Parameter                                                 | Symbol                            | Min | Тур | Max | Units |

|-----------------------------------------------------------|-----------------------------------|-----|-----|-----|-------|

| Peak bias current into V <sub>CC</sub> pin <sup>[1]</sup> | I <sub>cc</sub> Peak              | 0   |     | 10  | mA    |

| V <sub>CC</sub> bias resistor                             | R <sub>cc</sub>                   | 100 |     | 360 | kΩ    |

| V <sub>CC</sub> bypass supply capacitor                   | Cvcc                              | 2.2 |     | 3.3 | μF    |

| S <sub>REF</sub> Resistor                                 | R <sub>SERF</sub>                 | 9   |     | 11  | kΩ    |

| Sense reference filter capacitor                          |                                   | 22  |     | 47  | μF    |

| Line-Load sense resistors                                 | R <sub>IN</sub> /R <sub>OUT</sub> | 2.2 |     | 3.3 | MΩ    |

| DRV pin load capacitance                                  | DRV <sub>C-LOAD</sub>             |     |     | 30  | nF    |

| Ambient Operating Temperature                             | Тамв                              | -40 |     | 105 | °C    |

| Votes:                                                    |                                   | •   | •   |     | •     |

#### Table 3 Recommended Operating Conditions

1. Icc peak current applies to worst case maximum continuous VAC peak voltage: (VAC peak voltage -18V)/Rcc

#### Table 4 Electrical Characteristics

| Parameter                            | Conditions                                       | Min  | Тур  | Max  | Units  |

|--------------------------------------|--------------------------------------------------|------|------|------|--------|

|                                      | Rising Condition (V <sub>cc</sub> OK)            | 13.8 | 14.6 | 15.4 | V      |

| V <sub>cc</sub> UVLO                 | Falling Condition (V <sub>cc</sub> Fault)        |      | 13.3 |      | V      |

|                                      | Hysteresis Condition (V <sub>cc</sub> OK, Fault) |      | 1.3  |      | V      |

|                                      | lvcc=1 mA                                        |      | 17.6 |      | V      |

| V <sub>CC</sub> CLAMP                | I <sub>VCC</sub> =10 mA                          |      | 18.2 |      | V      |

| I <sub>ENERGIZE</sub>                | Ivcc Startup Current (min)                       | 40   | 60   | 80   | µA rms |

| T <sub>ENERGIZE</sub>                | VAC = 230 V RMS 50 Hz (start- up time)           |      | 0.4  |      | sec    |

| V <sub>SERF</sub>                    | Regulated voltage in normal condition            | -5%  | 2.0  | +5%  | V      |

| V <sub>STARTMAX</sub> <sup>[1]</sup> | V <sub>SNS</sub> -V <sub>SREF</sub>   absolute   | -6%  | 1.5  | +6%  | V      |

| OVP <sub>TRIP</sub> <sup>[2]</sup>   | V <sub>SNS</sub> -V <sub>SREF</sub>   absolute   | -5%  | 1.6  | +5%  | V      |

| T <sub>CT</sub>                      | 1 nF from CT to COM (timing delay)               |      | 0.8  |      | sec/nF |

| I <sub>CT</sub>                      | Source/Sink Current (timing current)             | 6    | 9    | 12   | μA     |

| T <sub>DRV_HI</sub>                  | 10 % to 90 % (high rise timing)                  |      | 6    |      | μs     |

| DRV <sub>LO</sub>                    | IGBT gate discharge (sink current)               |      | 20   |      | mA     |

| DRV <sub>ROL</sub>                   | DRV < 0.6 V (off state resistance)               |      | 10   |      | Ω      |

| RIN <sub>CL</sub>                    | I <sub>RIN</sub> = ± 1 mA (clamp voltage)        | 0.3  |      | 4.4  | V      |

| Parameter              | Conditions                                          | Min   | Тур | Max  | Units |

|------------------------|-----------------------------------------------------|-------|-----|------|-------|

| ROUT <sub>CL</sub>     | I <sub>RIN</sub> = ± 1 mA (clamp voltage)           | 0.3   |     | 4.4  | V     |

| SNS <sub>CL</sub>      | I <sub>SNS</sub> = ± 1 mA (clamp voltage)           | 0.3   |     | 4.4  | V     |

| I <sub>LEAK_RIN</sub>  | -40 mV < V <sub>RIN</sub> <+40 mV (leakage current) | -0.05 | 0   | 0.05 | μA    |

| I <sub>LEAK_ROUT</sub> | 40 mV < V <sub>ROUT</sub> <+40 mV (leakage current) | -0.05 | 0   | 0.05 | μA    |

| I <sub>LEAK_SNS</sub>  | +0.2 V < V <sub>SNS</sub> <+3.8 V (leakage current) | -0.05 | 0   | 0.05 | μA    |

| TSDJUNCTION            | Drive pin low                                       |       | 150 |      | °C    |

| TSD <sub>HYST</sub>    |                                                     |       | 25  |      | °C    |

Notes:

1. VAC peak input voltage for figure 1 circuit load startup = V<sub>STARTMAX</sub>\* (R<sub>SNS</sub>+R<sub>SERF</sub>) / (R<sub>SERF</sub>) peak = ~ 438 Vpk = ~310 V RMS 2. VAC peak input voltage for figure 1 load isolation = OVP<sub>TRIP</sub>\* (R<sub>SNS</sub>+R<sub>SERF</sub>) / (R<sub>SERF</sub>) peak = ~ 467 Vpk = ~330 V RMS

#### Table 5 ESD Ratings

| Parameter                                                | Value | Units |

|----------------------------------------------------------|-------|-------|

| Human Body Model (HBM), per Joint JEDEC/ESDA JS-001-2017 | ±2    | kV    |

| Charged Device Model (CDM), Joint JEDEC/ESDA JS-002-2018 | ±1    | kV    |

| Latch-up Immunity, JESD78E, Class 2, +125 °C             | ±100  | mA    |

# Table 6 Thermal Characteristics

| Thermal Resistance | θ <sub>JA</sub> | <b>θ</b> <sub>JC</sub> | Units |

|--------------------|-----------------|------------------------|-------|

| SOIC-8             | 170             |                        | °C /W |

## **3 Functional Description**

The AU8530 is an AC switch controller that instantly cuts off incoming AC power in the event that imminent over voltages are detected, thereby preventing the load from being sustained above its maximum ratings

#### Figure 3 Functional Block Diagram

The load is reconnected and regular functioning begins after the incoming AC power voltage has leveled to values that are safe. The 'connect/disconnect' function of the AC switch is always synced to the OV (zero volt) Line-to-load state, which prevents excessive in-rush currents and inductive "kick-back" spikes. The external component values, CT and RSNS, let the user to alter the stabilization timer interval (CT delay) and over-voltage protection (OVP) level.

## 3.1 VCC PIN

The supply bias voltage, or V<sub>CC</sub> pin, of the AU8530 has an undervoltage lockout circuitry (UVLO) built-in to prohibit activation until sufficient voltage is present to run the external IGBTs. The device can start operating normally when the typical input supply bias current exceeds UVLO, which is only 60  $\mu$ A rms. With the component values (R<sub>CC</sub> of 360 k) displayed in Figure 1, the UVLO level can be reached at about 60 V rms of VAC input.

Selecting alternative, higher or lower, values for  $R_{CC}$  bias resistor will accordingly adjust the nominal VAC input voltage at which the UVLO level is achieved. Any additional Icc current injected into the Vcc pin will be safely clamped once V<sub>CC</sub> rises to 17.5 V. The peak V<sub>CC</sub> pin current is recommended to be less than 10 mA.

#### Figure 4 VCC Operating and Clamping Current

### 3.2 SERF PIN

For the purpose of providing a precise AC reference for detecting over-voltage events, the S<sub>REF</sub> pin has an inbuilt 2 V regulator. The external resistor (9 k $\Omega \sim$  11 k $\Omega$  range) connected to the SNS pin and an external capacitor (22  $\mu$ F  $\sim$  47  $\mu$ F range) connected to the COM pin are needed for the S<sub>REF</sub> pin.

There is a slight offset shift from the nominal Over Voltage Protection (OVP) goal setting as a result of the 2 V bias reference at the  $S_{REF}$  pin. Generally, negative OVP events will cause 2 V to be raised, and positive OVP events will cause 2 V to be lower than the design target. At OVP settings of around 330 V rms (267 V peak), the deviation from the nominal design desired result is less than 0.5%.

### 3.3 RIN/ROUT PINS

The circuitry required to detect the zero-voltage situation across the AC switch—which synchronizes the AC switch turn-on/off events—is contained in the  $R_{IN}/R_{OUT}$  pins. Furthermore, active current clamp circuitry is incorporated into both  $R_{IN}/R_{OUT}$  pins to guarantee that their voltage levels remain within safe working limits.

When the AC switch is in the off position, the maximum current clamping level into either pin happens at the VAC peak positive phase for the R<sub>IN</sub> pin and the VAC peak negative phase for the R<sub>OUT</sub> pin.

To enable the system to manage VAC peak voltages above 2 kV, external resistor values for  $R_{IN}/R_{OUT}$  resistors should be set within the range of 2.2 M $\Omega$  to 3.3 M $\Omega$  when current clamping levels exceed 1 mA. When 3.3 M $\Omega$  external resistors are employed, the pin capacitance of  $R_{IN}$  and  $R_{OUT}$  is approximately 5 pF, resulting in a time constant delay of around 15  $\mu$ s.

### 3.4 SNS PIN

The SNS pin serves as the input voltage for over-voltage protection and is connected to the  $S_{REF}$  pin by a nominal resistor with a value of 10 k $\Omega$ . The AC-switch turn-on procedure begins when the peak voltage differential between SNS and  $S_{REF}$  falls within ±1.5 V during initial start-up or over-voltage recovery.

When the device is in normal operation, with AC-switch turned-on, an over-voltage event will be detected if the peak voltage difference between SNS and  $S_{REF}$  exceeds the range of ±1.6 V (i.e. SNS input voltage exceeds 3.6 V or falls below 0.4 V), at which point the AC switch is turned-off upon the next O V Line-to-load event. A phase positive over-voltage event, will turn-off the AC- switch on the falling edge of Line-to-load zero voltage and a negative phase over-voltage event will turn-off the AC-switch on a rising edge of Line-to-load zero voltage.

Start-up VAC peak < 1.5V x (Rsns + Rsref)/Rsref (V)

OVP trip VAC peak > 1.6V x (Rsns + Rsref)/Rsref (V)

For the component values as shown in Figure 1, this equates to:

Start-up VAC peak < 1.5V x 2920k/10k = 438 (V) < 315V RMS

OVP trip VAC peak > 1.6V x 2920k/10k = 467 (V) > 330V RMS

The SNS pin input also contains internal active current clamping circuitry in the event of extreme over-voltage conditions that can safely clamp current level in excess of 1 mA.

### 3.5 CT PIN

By using the CT pin, the user can program a timing interval (CT delay) during which the VAC voltage needs to be kept stable and below the maximum start-up voltage. Following one complete cycle in which the VAC is inside the start-up voltage range, the timer starts to run. This holds true for OVP recovery as well as the initial power-up state. The total timer duration is set via an external capacitor placed between the CT pin and the COM pin.

The CT timing circuitry progressively ramps the external capacitor between 3.7 V and 0.3 V and back to 3.7 V through an internal pull-down current of 9  $\mu$ A and an external pull-up current of 9  $\mu$ A. During 1024 cycles, this sequence yields an overall timer coefficient of 0.8 sec/nF.

$$= 1024 \text{ x} 3.4 \text{ x} 2 \text{ x} \text{ CT} (\text{F}) / 9u = 0.774 \text{ sec/nF}$$

Following the completion of the timer interval, the AC switch will be synchronized to activate at the subsequent zero voltage rising edge of the Line-to-load voltage.

When VAC goes beyond its permitted start-up voltage during the timer interval, the timer will be reset and wait for the next full cycle in which VAC is back within its start-up voltage before it is reactivated.

### 3.6 DRV PIN

The AU8530's DRV pin provides the voltage required to sufficiently operate the external high voltage back-toback IGBTs that make up the AC switch. An Nfet "voltage follower" in the internal circuitry drives the output to within 0.75 V of the V<sub>CC</sub> voltage. The DRV voltage output will likely proceed to 17.5 V during severe V<sub>CC</sub> current clamping conditions and fall to 13 V when the V<sub>CC</sub> level returns to UVLO.

It's not necessary to run the IGBTs very quickly because the AC switch's on/off function is always coordinated with its zero-voltage state.

The DRV output ramps smoothly across a 6  $\mu$ s time interval for IGBT turn-on events, regardless of the external capacitive load. In order to safely drive IGBTs into their "off" state within 8 seconds, the DRV pin discharges via a 20 mA current sink during IGBT turn-off events. At that point, 10  $\Omega$  internal pull-down is triggered when the DRV voltage drops below 0.6 V.

Reverse current from the DRV pin to the V<sub>CC</sub> pin can also travel through an internal power diode in the DRV circuitry. This makes sure the DRV voltage output will always be low enough to avoid IGBT turn-on situations during the AU8530 first power-up, while V<sub>CC</sub> is still or almost O V.

## **4 Thermal Dissipation**

The AU8530 thermal dissipation is primarily determined by the levels of Vcc clamping current.

A half-sine wave with a maximum peak current of 10 mA is the clamping current into V<sub>CC</sub> under the maximum parameters shown in Table 3, with the ambient operating temperature being +105 °C. An average clamping current of 3.75 mA (50% x 10 mA /  $\sqrt{2}$ ) would equal the VCC voltage, which would normally be 18 V. It will dissipate power on average of:

$Pdiss = 18V \ge 3.75mA = 68Mw$

Using the SOIC-8 package junction to ambient thermal resistance (ThetaJA) of 170 °C/W, the resulting junction temperature with 68 mW dissipation at +105 °C ambient would be:

Tjunct = Pdiss x ThetaJA + Tambient = 68mW x 170°C /W + 105°C = 12°C + 105°C = 117°C

When the junction exceeds 150 °C, an exceptional case of thermal overload occurs, in which case the load is separated at the next Line-to-load zero voltage event falling edge. The standard start-up procedure will begin instantly as the junction temperature drops below 125 °C once more.

Figure 8 Over-Voltage Protection Timing Example

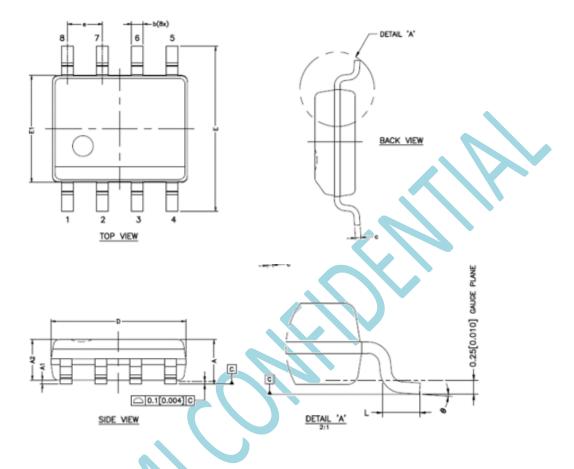

# **5 Package Description**

Figure 9 AU8530 SOIC 8

|        | Millimetres |      | Inc       | ches  |

|--------|-------------|------|-----------|-------|

| Symbol | Min         | Max  | Min       | Мах   |

| A      | 1.35        | 1.75 | 0.053     | 0.069 |

| A1     | 0.10        | 0.25 | 0.004     | 0.010 |

| A2     | 1.25        | 1.50 | 0.049     | 0.059 |

| b      | 0.35        | 0.49 | 0014      | 0.019 |

| C      | 0.19        | 0.25 | 0.007     | 0.010 |

| D      | 4.80        | 5.00 | 0.189     | 0.197 |

| E      | 5.80        | 6.20 | 0.228     | 0.244 |

| E1     | 3.80        | 4.00 | 0.150     | 0.157 |

| е      | 1.27 BSC    |      | 0.050 BSC |       |

| L      | 0.40        | 1.27 | 0.016     | 0.050 |

| θ      | 0°          | 80   | 0°        | 8°    |

Note: All dimensions shown are in millimetres (mm) unless otherwise noted.

# **6 Ordering Information**

#### Table 7 AU8530 Ordering Information

| Ordering Part Number (OPN) | Marking | Package information | Temperature<br>Range | MSL |

|----------------------------|---------|---------------------|----------------------|-----|

| AU8530                     | AU8530  | SOIC-8              | -40 °C to 105 °C     | 1   |

Note: This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive 2015/863/EU.

## 6.1 Top Marking

TBD

Figure 10 AU8530 Top Marking

# 7 Revision History

### Table 8 Revision History

| Version<br>Number | Date                      | Description              | Author   |

|-------------------|---------------------------|--------------------------|----------|

| 1.0               | 28 <sup>th</sup> Aug 2024 | AU8530 Datasheet created | Aurasemi |

www.aurasemi.com

#### IMPORTANT NOTICE AND DISCLAIMER

AURASEMI PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Aurasemi products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Aurasemi grants you permission to use these resources only for development of an application that uses Aurasemi products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Aurasemi intellectual property or to any third-party intellectual property. Aurasemi disclaims responsibility for, and you will fully indemnify Aurasemi and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Aurasemi products are provided only subject to Aurasemi Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Aurasemi resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

### **Contact Information**

For more information visit www.aurasemi.com For sales related information please send an email to sales@aurasemi.com

#### Trademarks

All referenced brands, product names, service names and trademarks are the property of their respective owners.